|

Belle II Software development

|

|

Belle II Software development

|

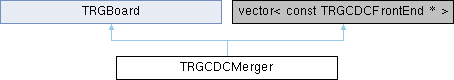

A class to represent a CDC merger board. More...

#include <Merger.h>

Public Types | |

| enum | unitType { innerType = 0 , outerType = 1 , unknown = 999 } |

| enum of unitType More... | |

Public Member Functions | |

| TRGCDCMerger (const std::string &name, unitType type, const TRGClock &systemClock, const TRGClock &dataClock, const TRGClock &userClockInput, const TRGClock &userClockOutput) | |

| Constructor. | |

| virtual | ~TRGCDCMerger () |

| Destructor. | |

| unitType | type (void) const |

| return type. | |

| void | simulate (void) |

| simulates firmware. | |

| void | push_back (const TRGCDCFrontEnd *) |

| push back TRGCDCFrontEnd of this Merger | |

| void | dump (const std::string &message="", const std::string &pre="") const |

| dumps contents. "message" is to select information to dump. "pre" will be printed in head of each line. | |

| void | dump_log (void) const |

| Dump all the details of _mosb into a .log file, do it in the end of simulate() | |

| void | dump_log_inner (void) const |

| dump_log for inner Merger | |

| void | dump_log_outer (void) const |

| dump_log for outer Merger | |

| const std::string & | name (void) const |

| returns name. | |

| const TRGClock & | clockSystem (void) const |

| returns system clock. | |

| const TRGClock & | clockData (void) const |

| returns data clock. | |

| const TRGClock & | clockUserInput (void) const |

| returns Aurora user clock for input. | |

| const TRGClock & | clockUserOutput (void) const |

| returns Aurora user clock for output. | |

| unsigned | nInput (void) const |

| returns input channels. | |

| const TRGChannel * | input (unsigned i) const |

| returns input channel i. | |

| unsigned | nOutput (void) const |

| returns output channels. | |

| TRGChannel * | output (unsigned i) const |

| returns output channel i. | |

| void | appendInput (const TRGChannel *) |

| appends an input Aurora channel. | |

| void | appendOutput (TRGChannel *) |

| appends an output Aurora channel. | |

Static Public Member Functions | |

| static std::string | version (void) |

| return version. | |

| static TRGState | packerInner (const TRGState &input) |

| Make bit pattern using input information from inner FEs. | |

| static TRGState | packerOuter (const TRGState &input) |

| Make bit pattern using input information from outer FEs. | |

| static void | unpackerInner (const TRGState &input, const TRGState &output) |

| Unpack TRGState. | |

| static void | unpackerOuter (const TRGState &input, const TRGState &output) |

| Unpack TRGState. | |

| static int | implementation (const unitType &type, std::ofstream &) |

| make a VHDL component file. | |

| static int | implementationPort (const unitType &type, std::ofstream &) |

| writes a port map. | |

Public Attributes | |

| TRGSignalBundle * | mosb = nullptr |

| Output signal bundle. not the best way to do this though. | |

| T | elements |

| STL member. | |

Private Attributes | |

| unitType | _type |

| Unit type. | |

| TRGSignalBundle * | _misb |

| Input single bundle. | |

| TRGSignalBundle * | _mosb |

| outptu signal bundle | |

| const std::string | _name |

| Name of a board. | |

| const TRGClock * | _clockSystem |

| System clock. | |

| const TRGClock * | _clockData |

| Data clock. | |

| const TRGClock * | _clockUserInput |

| User clock. | |

| const TRGClock * | _clockUserOutput |

| User clock. | |

| std::vector< const TRGChannel * > | _inputChannels |

| Input Aurora channel. | |

| std::vector< TRGChannel * > | _outputChannels |

| Output Aurora channel. | |

| enum unitType |

|

privateinherited |

|

privateinherited |

|

private |

|

private |

|

privateinherited |

| TRGSignalBundle* mosb = nullptr |